## 彌補微影技術限制 高速、多功能 DFM 技術嶄露頭角

DFM(**d**esign **f**or **m**anufacturability)技術能將電路布局改成更容易曝光的形狀，其重要性已不言可喻。65nm 製程節點(hp90)以下，光憑改善曝光過程，並無法使電路布局的解晰度達到最高。在 2006 年 2 月舉辦的國際曝光技術會議中，除有眾多發表 DFM 方案相關論文的技術人員與會之外，新興 EDA 領域的代理廠商，也相繼發表高速、多功能的曝光模擬技術。LSI 的先行廠商，將這些關鍵技術予以整合，相繼完成整體設計和製程。其中最受矚目的是能預測電路布局解晰度不佳的位置，予以校正及管理的製程。

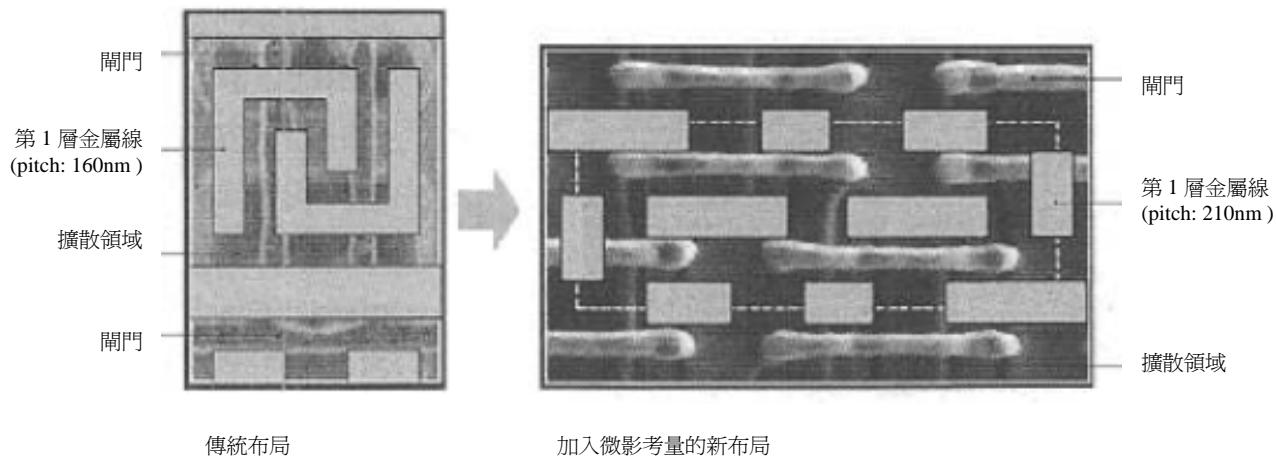

考量微影技術，SRAM 電路布局單純化實例。資料來源：美國 Intel Corp.

註 1) 這意味著 DFM 是代表「design for money」的意思。

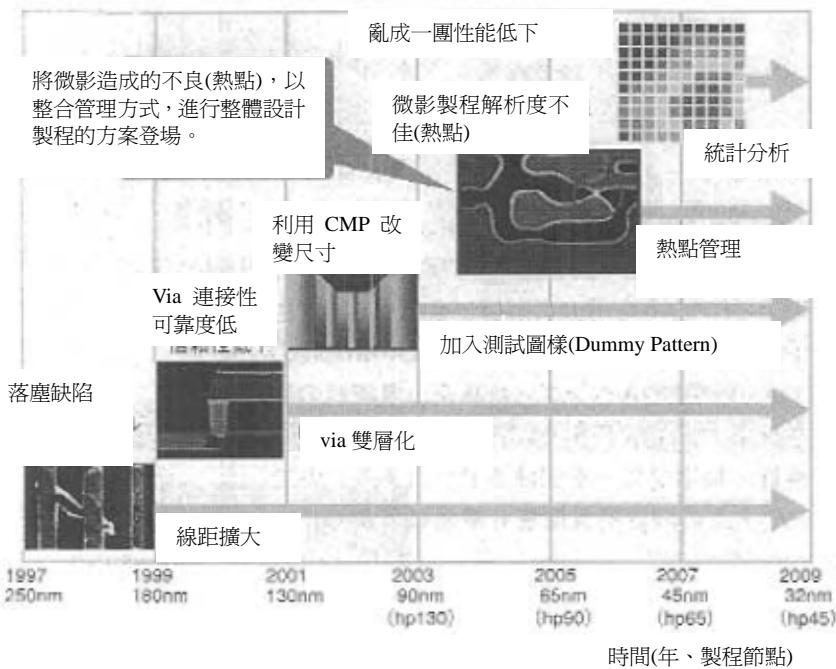

能彌補微影技術限制的 DFM (design for manufacturability) 技術，使成品良率提高(圖 1)。先發端的 LSI 廠商，藉由整合關鍵技術，完成整體設計和製程。迄今一直和 LSI 廠商合作開發 DFM 技術的 EDA 代理商，本成果所製造的新產品，也開始進入銷售階段。未來，

圖 1 ● 65nm 製程節點以下，微影造成的問題浮上檯面

以往是針對落塵和配線的問題，但現在開始要面對的是微影限制的挑戰。資料來源：

本刊根據美國 Synopsys, Inc. 資料製作。

將面臨需進一步提升微細化程度的 DFM 流程挑戰。因此，開始嚴格限制電路線距種類和配線方向，以讓微影技術有更多的發揮空間的行動。

### 65nm 以下微影製程面 DFM 為必要條件

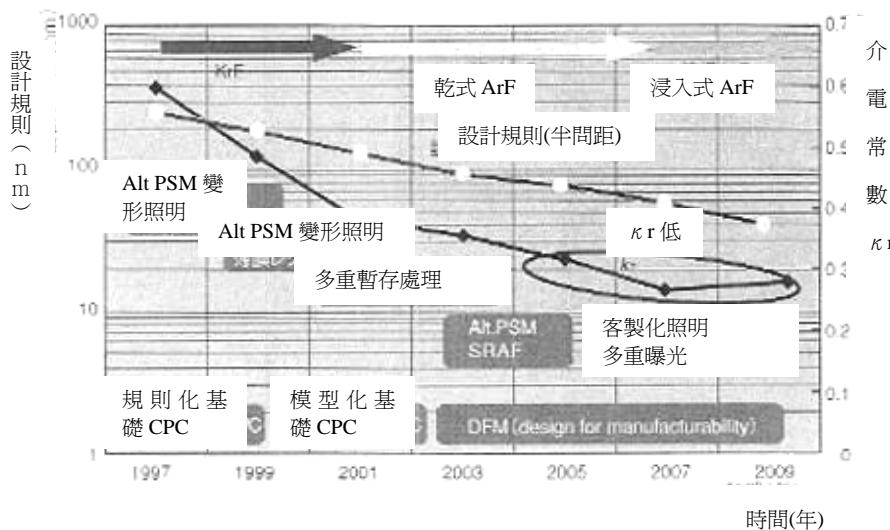

DFM 是能彌補製程限制的設計技術通稱，內容會因不同的微細化程度而異。到目前為止，最重要的即屬微影面的 DFM 技術。目前的微影技術，在微細化的要求條件下，基本解晰能力不足(圖 2)。為彌補這項缺失，採用相移光罩等超高解析技術。然而，超高解析技術，在圖樣中大多數的線寬/線距呈規則時能發揮效用，但對「複雜的 2 維圖樣莫可耐何」(NEC Electronics 笠間邦彥 高級專員)。因此，65nm 製程節點(hp90)以下在曝光時，圖樣會有部分被切掉、造成尺寸變小的問題急速增加。

能因應微影限制的 DFM，在設計階段即可預測上述這種解析度不佳的位置，藉由改變電路布局，讓該些位置消失無蹤。並且，一開始就製作出可供超高解析技術，充分發揮的規則性電路布局。以上任何一種情況，都是朝減少設計彈性、增加晶片面積的方向發展，但是可以有效提升良率，故整體而言仍可降低成本<sup>註 1)</sup>。

今年 2 月在美國舉辦的「31<sup>st</sup> International Symposium Microlithography」國際會議中，先發端的 LSI 廠商，發表因應微影限制 DFM 的全貌。其中最受矚目的是東芝在 65nm 製程節點所引進的 DFM 流程(圖 3)。對於電路布局上難以辨識的「熱點(hot spot)」部分，設計排除機制，於製程整合監視熱點的機制設計。

圖 2 ● 微影技術基本解析能力不足

微影技術的製程係數介電常數  $\kappa_r$  很低，即表示微影製程面的難度增加。資料來源：

東芝。